Imec develops functional 5nm BEOL solution

Article By : Imec

Imec is tackling shrinking interconnect challenges, including RC delays, with a full dual-damascene module that incorporates multi-patterning and multi-blocking.

As R&D progresses towards the 5nm technology node, the tiny Cu wiring schemes in the chips’ back-end-of-line (BEOL) are becoming increasingly complex and compact. To address that challenge, Imec has announced an electrically functional solution, which is a full dual-damascene module in combination with multi-patterning and multi-blocking. Scaling boosters and using aggressive design rules pave the way to even smaller dimensions.

Shrinking the dimensions also reduces the wires cross-sectional area, driving up the resistance-capacitance product (RC) of the interconnect systems and thus increasing signal delay. One viable option is to extend the Cu-based dual-damascene technology—the current workhorse process flow for interconnects—into the next technology nodes.

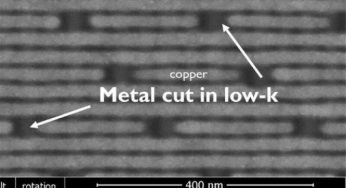

Imec has demonstrated that the 5nm BEOL can be realised with a full dual-damascene module using multi-patterning solutions. With this flow, trenches are created with critical dimensions of 12nm at 16nm. Metal-cuts (or blocks) perpendicular to the trenches are added in order to create electrically functional lines and then the trenches are filled with metal. Area scaling is further pushed through the introduction of fully self-aligned vias. Moreover, aggressive design rules are explored to better control the variability of the metal tip-to-tips (T2Ts).

Figure 1: Dense-pitch blocks enabled by a dual damascene flow and multi-patterning. The pattern is etched into the low-k and metallised.

Beyond 5nm, Imec is exploring alternative metals that can potentially replace Cu as a conductor. Among the candidates identified, low-resistive Ruthenium (Ru) has demonstrated great promise. The Imec team has realised Ru nanowires in scaled dimensions, with 58nm² cross-sectional area, exhibiting low resistivity, robust wafer-level reliability and oxidation resistance, eliminating the need for a diffusion barrier.

Tackling RC delay

“The emergence of RC delay issues started several technology nodes ago and has become increasingly more challenging at each node. Through innovations in materials and process schemes, new BEOL architectures and system/technology co-optimisation, we can overcome this challenge as far as the 5nm node”, said Zsolt Tokei, Imec’s nano-interconnect program director. “Imec and its partners have shown attainable options for high density area scaled logic blocks for future nodes, which will drive the supplier community for future needs.”

For the longer term, Imec is investigating different options, including but not limited to alternative metals, insertion of self-assembled monolayers or alternative signalling techniques such as low-energy spin-wave propagation in magnetic waveguides, exploiting the electron’s spin to transport the signal. For example, the researchers have experimentally shown that spin waves can travel over several micrometres, the distance required by short and medium interconnects in equivalent spintronic circuits.

Subscribe to Newsletter

Test Qr code text s ss