Synopsys compiles low-power ref. kit

Article By : Vivek Nanda

The kit is based on a bitcoin mining SoC and is designed aid deployment of a Unified Power Format-based hierarchical design methodology.

Synopsys Inc. has announced a comprehensive low-power reference kit for design and verification based on a bitcoin mining SoC design. The detailed low power flow and accompanying reference kit covers all aspects of a typical SoC design flow, stepping through all phases from RTL creation through final signoff. It is specifically designed to help accelerate deployment of a Unified Power Format (UPF)-based hierarchical design methodology by providing all design views with built-in templates and scripts spanning more than 15 Synopsys products.

The kit can also be used as a learning vehicle for the Synopsys low power flow. Modular in nature, it helps with incremental adoption of a specific or broader-range of tools so that you can focus on specific functional areas, such as verification or implementation.

The reference kit includes a user guide that provides step-by-step instructions for the individual tools used during various stages of a low power design flow.

Products covered by the low power reference kit include:

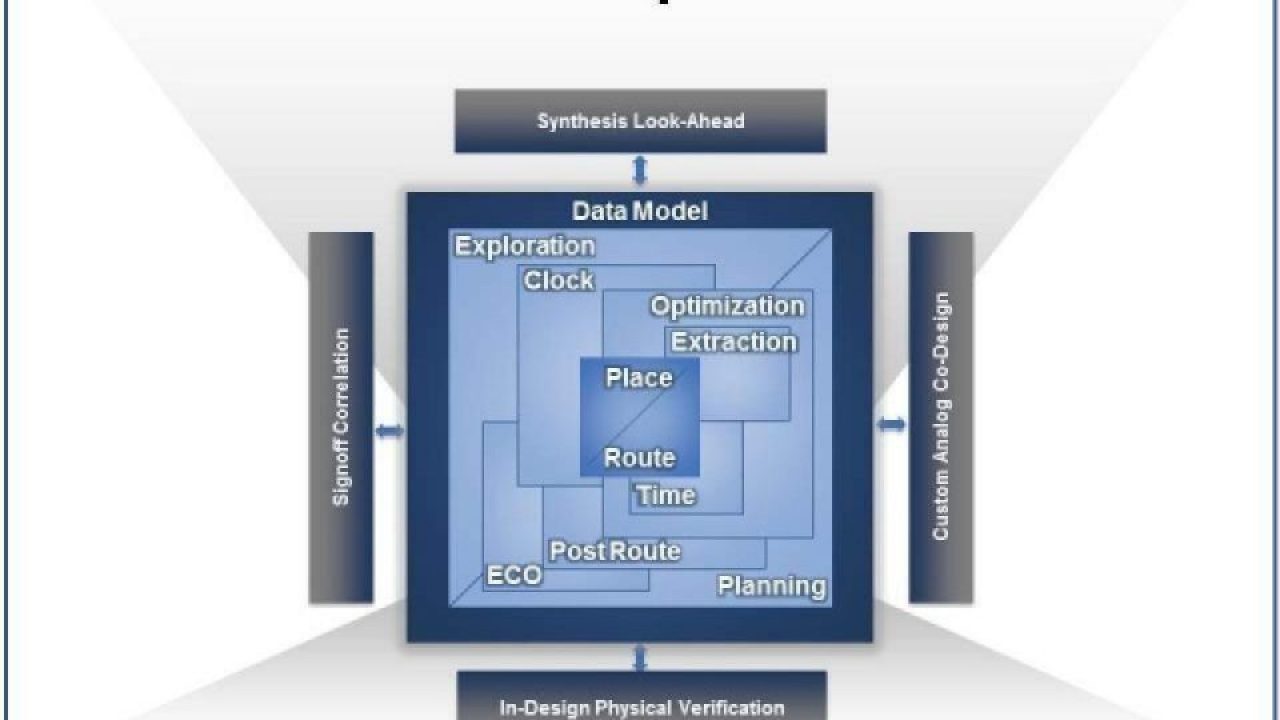

- IC Compiler II place and route system

- Design Compiler RTL synthesis product family

- DFTMAX and TetraMAX II test solutions

- Formality formal verification tool

- PrimeTime and PrimeTime PX timing and power signoff

- StarRC extraction solution

- VCS native low power simulation

- Verdi automated debug system

- SpyGlass static verification tool

- VC LP low power static verification

Synopsys is launching the kit today at its Synopsys User's Group (SNUG) event in Santa Clara, California.

Subscribe to Newsletter

Test Qr code text s ss