Intel Demonstrates 3D Packaging Technology Foveros

Article By : Dylan McGrath, EE Times

Two decades of research culminates in 3D stacking of high-performance chips

LOS ALTOS, Calif. — Intel demonstrated a new 3D packaging technology for face-to-face stacking of logic, scheduled to be available in the second half of next year. The company also tipped a new processor microarchitecture and a new graphics architecture on a day when its chief architect laid out the company’s vision for future computing architectures.

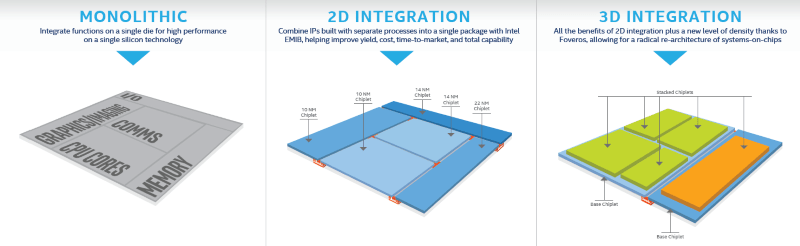

The 3D packaging technology, known as Foveros, is the culmination of two decades of research at Intel into stacking die in three-dimensional heterogeneous structures combining logic and memory. Unlike the passive interposer and stacked memory technologies currently available, Foveros extends the 3D packaging concept to include high-performance logic such as CPU, graphics and AI processors.

“We are doubling down on our process and advanced packaging leadership,” said Raja Koduri, Intel’s chief architect and senior vice president of its Core and Visual Computing group.

Referencing the semiconductor industry’s quest to connect different chips and chiplets in integrated 3D packages, Koduri added, “We have finally figured out how to make this a real, manufacturable thing,”

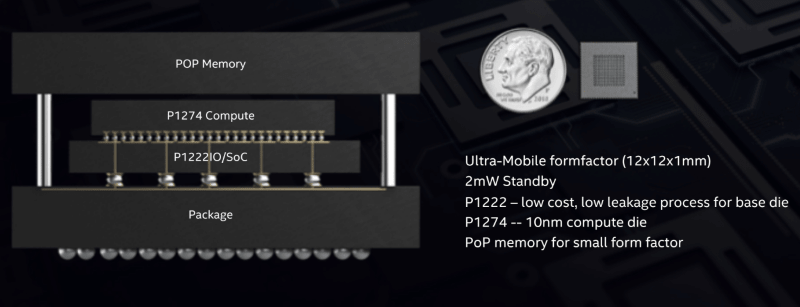

Koduri said Intel has already built products using the Foveros technology in response to customer requests. At the event, he showed what he called the first hybrid x86 architecture, featuring 10nm logic chiplets and 22nm base die and memory in a 12x12x1mm Foveros package drawing just 2mW of standby power.

First Hybrid x86 Architecture (Source: Intel)

According to Koduri, Foveros technology will give designers greater flexibility to mix and match IP blocks with various memory and I/O elements in new form factors. He said the company plans to leverage the technology across the entire Intel product line.

Koduri unveiled Foveros at a press event in a home that was originally built for Robert Noyce, one of Intel’s founders. Over the course of a two-hour presentation, he sketched out the company’s vision for its architecture roadmap in an era when the paradigms of computing are changing rapidly and traditional process scaling is running out of gas.

Koduri predicted that architectures would define this era of computing. He said that over the next 10 years there would be more innovation in computing architectures than there has been in the last 50 years combined.

“We are going to architect our way around the slopes in this era,” he said.

Intel says having 2D and 3D packaging technologies gives it flexibly to combine smaller chiplets of IP to meet the demands of a range

of applications, power envelopes and form factors. (Source: Intel)

Koduri outlined a shift for Intel’s design and engineering model, built around six key pillars: process, architecture, memory, interconnect, security and software.

For Intel, Koduri said, Moore’s Law was always about more than just what increased density offered. Acknowledging the significant challenges to continued scaling, he added, “We need to innovate around physics. We need to innovate — not just for Intel’s sake, but for the Industry’s sake.”

In addition to the Foveros technology, Intel also used the occasion to unveil its next-generation CPU microarchitecture, codenamed “Sunny Cove.” It is designed to increase performance per clock and power efficiency for general purpose computing tasks, and includes new features to accelerate special purpose computing tasks like AI and cryptography.

According to the company, Sunny Cove offers greater parallelism and features new algorithms to reduce latency and larger buffers and caches to optimize data-centric workloads. It will be the basis for Intel’s next-generation Xeon and Core later next year.

In graphics, Intel unveiled its new Gen11 integrated graphics — to be delivered in 10nm-based processors next year — and sketched out plans for a brand new architecture — X<e> — to serve as the foundation for both integrated and discrete graphics chips starting in 2020.

Subscribe to Newsletter

Test Qr code text s ss