Samsung certifies Synopsys platform for 10LPP process

Article By : Synopsys

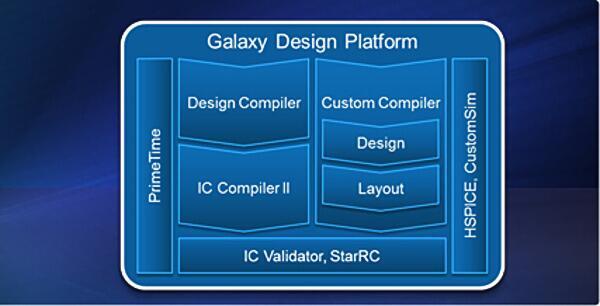

The Galaxy Design platform certification for Samsung's 10LPP process includes design techniques for enabling less power consumption.

Samsung Electronics has certified Synopsys Galaxy design platform for its second generation of 10nm low power plus (LPP) process.

The Galaxy certification for Samsung's 10LPP process includes design techniques for enabling less power consumption such as multibit register optimisation, low-power placement and In-Design rail and power analysis, all of which have been deployed on production designs at Samsung's 10LPP process.

Synopsys' SiliconSmart library characterisation tool was used to develop the foundation IP used for the certification process and reference flow. The certification also includes a reference flow, compatible with Synopsys' Lynx Design System, which includes scripts for automation and design best practices.

The reference flow of 10LPP process is compatible with Synopsys' Lynx Design System, a full-chip design environment that includes innovative automation and reporting capabilities to help designers implement and monitor their designs. It includes a production RTL-to-GDSII flow that simplifies and automates many critical implementation and validation tasks, enabling engineers to focus on achieving performance and design goals.

Synopsys's Custom Compiler tool has also been certified to support Samsung's 10nm LPP process, which include providing and validating a Custom Compiler process design kit (PDK) in the industry-standard iPDK format.

The newly developed Samsung 10LPP iPDK includes all technology information needed to create schematics and layout for customer designs using the Custom Compiler tool with Samsung's 10LPP process. This comprehensive kit includes support for the Custom Compiler visually-assisted automation flow. Custom Compiler features enabled by the kit include full colouring for triple-patterning, fast placement of FinFET device arrays with the Symbolic Editor, in-design resistance and capacitance reporting during layout and high-performance in-design design rule checking (DRC).

Unified with Synopsys circuit simulation, physical verification and digital implementation tools, Custom Compiler technology provides Samsung 10LPP process users with a comprehensive custom design solution that reduces FinFET layout time.

The 10LPP iPDK kit is available on request from Samsung.

Subscribe to Newsletter

Test Qr code text s ss