RISC-V: The Road Ahead

Article By : Rick Merritt

The open-source architecture faces a long road through software standards from its beachhead as an SoC controller to use as a host processor.

SAN JOSE, Calif. — Now that RISC-V has established a beachhead as a deeply embedded controller in SoCs, it’s time to start asking the next question: Can this open-source instruction-set architecture (ISA) make the next big leap into being an alternative to Arm and the x86 as a host processor?

The short answer is yes, but it could take several years and there are plenty of pitfalls along the way. Essentially, the freewheeling open-source community behind RISC-V will need to develop and adhere to a wide range of system-level standards.

So far, Nvidia and Western Digital plan to use RISC-V controllers in their SoCs, and Microsemi will use it in a new FPGA. Andes, Cortus, and startup SiFive sell IP cores, and a handful of startups plan to launch mainly machine-learning accelerators using it.

RISC-V is in as many as 20 million fitness bands and smartwatches in China. In the U.S., SiFive has shipped more than 2,500 development boards using processors that it aims to sell as IP cores or as SoCs through its design services.

“The lowest-hanging fruit is the embedded space where the APIs are not exposed to programmers,” said Rick O’Connor, executive director of the non-profit RISC-V Foundation. “That’s the easiest thing to do, but there’s healthy activity in all segments.

“There are implementations in every facet of processor architecture from mobile to machine learning, servers, automotive, deeply embedded real-time systems for factory automation, and everything in between,” he said.

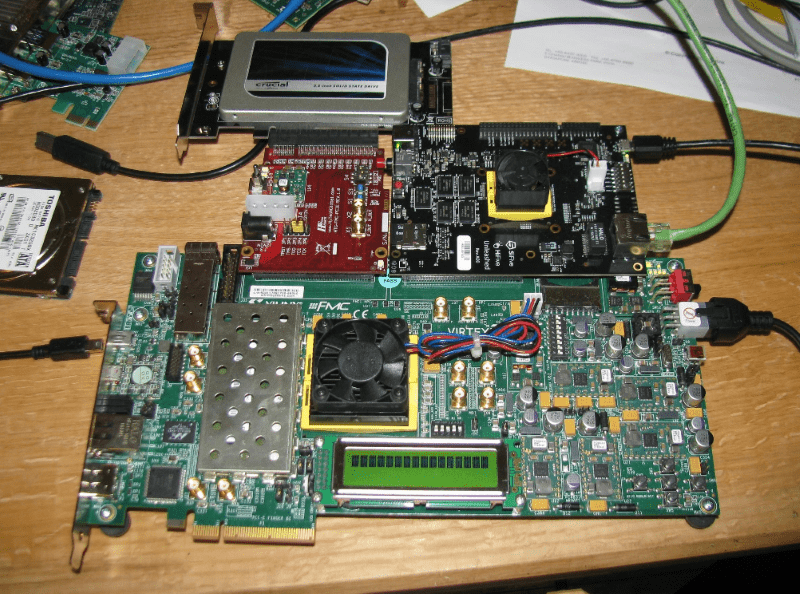

A SiFive development board linked to an FPGA board and SSD was used for a Fedora port. Click to enlarge. (Source: Richard W.M. Jones, Red Hat)

Although the ISA has been stable for months, it still lacks formal approvals. It’s core integer spec and at least some of a group of about a dozen other key specs will likely get ratified this year.

As soon as the specs are approved, the foundation aims to hammer out details of self-test compliance tests. Companies can run the tests to show that their products meet the specs.

As for software, a version of Fedora Linux is running on a SiFive Freedom Unleashed reference board, and several other Linux ports are in the works. A version of FreeBSD is available for RISC-V, and a Debian port is well underway. A Yocto embedded Linux port is in the works, as are versions of FreeRTOS and the open-source Zeyphr RTOS, said a RISC-V software expert at a talk in June.

The foundation just started work on a Linux boot spec, OpenSBI 0.1. Beyond Linux, there are no ports for Android, Windows, or other commercial OSes.

The bad news is that the OS ports are just the tip of a software iceberg.

A decade-long journey in host software

The OS ports are just the tip of a software iceberg, warns Jon Masters. He has spent the last nine years working on a standard version of Red Hat Linux for Arm servers. So far, just two commercial systems have been announced as certified to run it.

The process involved identifying a set of low-level hardware primitives that are assumed in the x86 world for things like how interrupts and power states work. Those de facto standards were articulated in a 50+ page document, then applied to the Arm architecture.

A separate effort documented x86 boot standards across Linux and Windows and applied them to Arm cores. They included obscure but crucial details of BIOS, power, and multiprocessing functions.

“I worry that the excitement of a new thing like RISC-V misses the real problems” of defining such support details, said Masters, who has been working on Linux for Arm servers since 2011.

RISC-V backers “will learn that no one got PCI right in Arm for the first few generations — to do PCI right [in a non-x86 host system] is tricky,” he said.

Server customers want support for both Windows and Linux, said Richard Jones, an emerging technologies specialist at Red Hat who worked on the RISC-V port of Fedora. In addition, they need a single image of an OS kernel and an applications binary interface that remains stable for years, Jones said in a talk at a RISC-V event last year.

A bootstrapped version of 64-bit Debian is available for RISC-V, but the architecture won’t be natively supported in the upcoming version 10 of the code. RISC-V still lacks support for an LLVM compiler, Java, and languages such as Golang and Rust, said a Debian developer at a recent event.

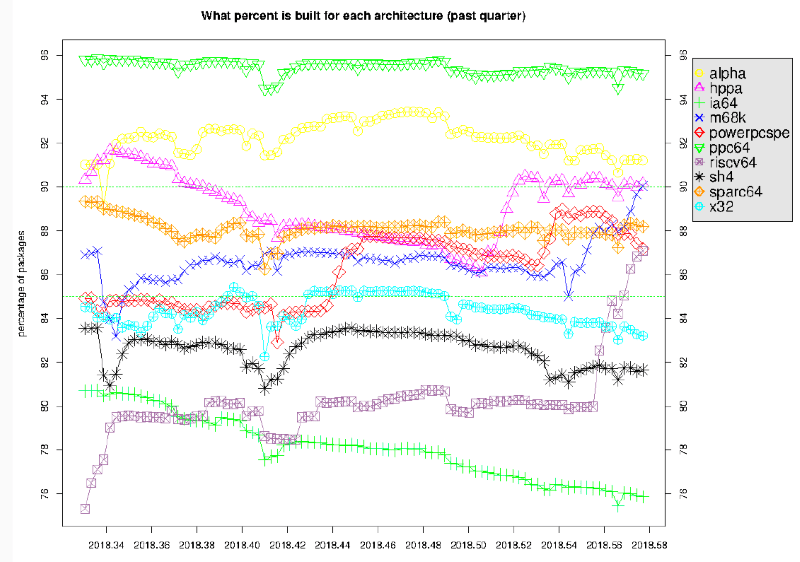

RISC-V is getting rising attention from Debian Linux developers. (Source: Karsten Merker)

For its part, Arm led the formation of Linaro, a collaboration that has worked for several years on low-level software for servers as well as systems for telcos and the internet of things. Linaro helped pave Arm’s expansion into a wide variety of areas but has required dedicated engineering time from a wide variety of members at an estimated cost of $100 million.

RISC-V “needs standards and something like a Linaro, and they know this,” said Masters.

China’s burgeoning interest in RISC-V could accelerate such efforts, perhaps collapsing them to a five-year journey. However, the opportunity for servers is arguably closing with two strong x86 companies and Arm server alternatives available from Ampere, Cavium, and Huawei, he said.

“Cloud server vendors are hedging their bets with Arm, but they don’t want 10 alternatives, so I’m not sure a RISC-V server opportunity really exists,” said Masters. “I’m sure startups will get funded, but I think they will build domain-specific accelerators.”

Community efforts storm software hurdles

RISC-V proponents say that the growing community of more than 100 organizations behind the open-source architecture is plowing through the software issues.

“I see no evidence of any adoption slowing down; I sign off on four or five membership agreements a week — it’s invigorating,” said O’Connor of his work at the foundation.

“We don’t have any plans for a Linaro-like effort, but that might change,” he said. The community has plenty of software development to do, but “there may be different ways to do it; Linaro had benefits and drawbacks,” including its cost, he added.

Meanwhile, individual efforts are working on many fronts in parallel, including an LLVM compiler and more RTOS support expected to be announced soon. Some of the work is not ISA-specific and may get done in collaboration with the Linux Foundation, he said.

“These things just take time — a couple years, perhaps 18 months,” said Naveed Sherwani, chief executive of SiFive. The startup has attracted customers who are large established systems or services companies creating their first chips and capable of writing software for them.

In addition, existing RISC-V backers such as “Microsemi and WD are assigning a lot of people to the software as well as the hardware side — a lot of partners are moving in parallel,” Sherwani said.

Subscribe to Newsletter

Test Qr code text s ss