Open acceleration framework improves data centre efficiency

Article By : AMD

For the first time in the industry, a single interconnect technology specification will ensure that processors using different instruction set architectures can coherently share data with accelerators and enable efficient heterogeneous computing.

Seven technology leaders have teamed up to bring an open acceleration framework to data centres.

Accelerating applications in the data centre has become a requirement due to power and space constraints. Applications such as big data analytics, search, machine learning, NFV, wireless 4G/5G, in-memory database processing, video analytics, and network processing, benefit from acceleration engines that need to move data seamlessly among the various system components.

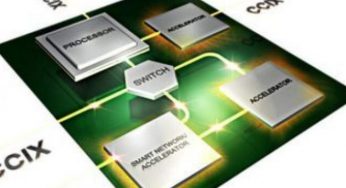

This was why AMD, ARM, Huawei, IBM, Mellanox, Qualcomm, and Xilinx collaborated to come up with a new framework, called Cache Coherent Interconnect for Accelerators (CCIX), which allows multiple processor architectures and accelerators to seamlessly share data.

For the first time in the industry, a single interconnect technology specification will ensure that processors using different instruction set architectures (ISA) can coherently share data with accelerators and enable efficient heterogeneous computing—significantly improving compute efficiency for servers running data centre workloads.

CCIX will allow the components to access and process data irrespective of where it resides, without the need for complex programming environments. This will enable both off-load and bump-in-the-wire inline application acceleration while leveraging existing server ecosystems and form factors, thereby lowering software barriers and improving total cost of ownership (TCO) of accelerated systems.

"A 'one size fits all architecture' approach to data centre workloads does not deliver the required performance and efficiency," said Lakshmi Mandyam, director server systems and ecosystems, ARM. "CCIX enables more optimised solutions by simplifying software development and deployment of applications that benefit from specialised processing and hardware offload, delivering higher performance and value to data centre customers."

"CCIX enables greater performance and connectivity capabilities over existing interconnects, and actually paves the road to the next generation CPU – Accelerator – Network standard interface," said Gilad Shainer, vice president of Marketing at Mellanox. "With an anticipated broad eco-system support of the CCIX standard, data centres will now be able to optimise their data usage, thereby achieving world-leading applications efficiency and scale."

"CCIX will leverage existing server interconnect infrastructure and deliver higher bandwidth, lower latency, and cache coherent access to shared memory," said Gaurav Singh, vice president of Architecture at Xilinx. "This will result in a significant improvement in the usability of accelerators and overall performance and efficiency of data centre platforms."

Subscribe to Newsletter

Test Qr code text s ss