Multi-core parallel engine powers Cadence simulator

Article By : Julien Happich

The Xcelium Parallel Simulator speeds runtime by an average of 3X for register-transfer level design simulation.

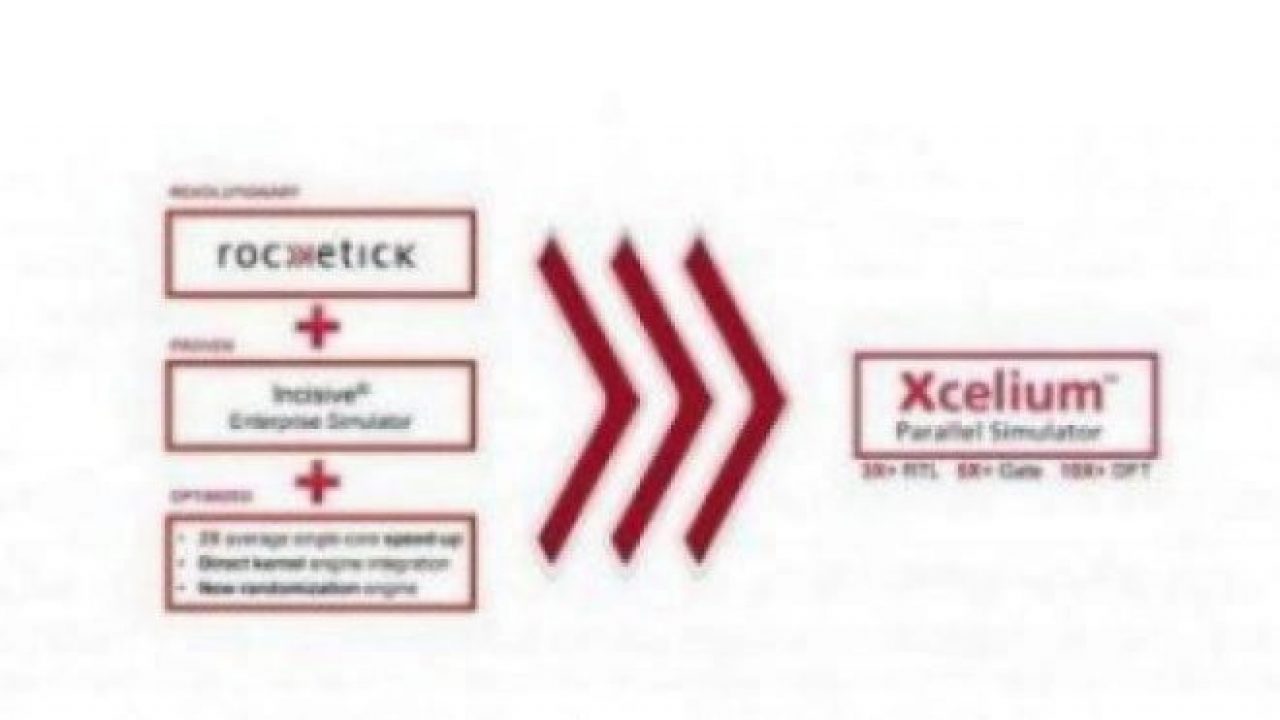

Cadence Design System has introduced the Xcelium Parallel Simulator, which the company claims is the industry's first production-ready simulator based on a multi-core parallel computing architecture.

The new simulator is said to help customers achieve 2X improved single-core performance and more than 5X improved multi-core performance versus the company's previous generation simulators.

Xcelium has already been deployed at early adopters across mobile, graphics, server, consumer, IoT and automotive projects. Built on the technology acquired from Rocketick, the new simulator speeds runtime by an average of 3X for register-transfer level (RTL) design simulation, 5X for gate-level simulation and 10X for parallel design for test (DFT) simulation, potentially saving weeks to months on project schedules, according to Cadence.

A new compilation and elaboration flow assigns the design and verification test bench code to the ideal engines and automatically selects the optimal number of cores for fast execution speed. New features that speed overall SoC verification time include SystemVerilog test bench coverage for faster verification closure and parallel multi-core build.

![[Cadence Protium (cr)]](/wp-content/uploads/sites/2/2020/04/Cadence_Protium_cr.jpg)

__Figure 1:__ *The Protium S1 FPGA-based prototyping platform.*

The EDA company announced the same day its Protium S1 FPGA-based prototyping platform for early software development built on Xilinx' Virtex UltraScale FPGAs to offer 6X higher design capacity and an average 2X performance improvement over Cadence's previous platforms.

The Protium S1 platform is compatible with the Cadence Palladium Z1 Enterprise Emulation Platform and its advanced memory modelling and implementation capabilities allow designers to reduce prototype bring-up from months to days. The platform shares a common compile flow with the Palladium Z1 platform, which enables up to 80% re-use of the existing verification environment and provides front-end consistency between the two platforms.

New firmware and software productivity-enhancing features include memory backdoor access, waveforms across partitions, force and release, and runtime clock control.

Subscribe to Newsletter

Test Qr code text s ss