Microsemi offers first open architecture RISC-V IP core

Article By : Microsemi

The RV32IM RISC-V core is available for Microsemi's IGLOO 2 FPGAs, SmartFusion 2 system-on-chip (SoC) FPGAs or RTG4 FPGAs.

Microsemi has become the first FPGA provider to offer a comprehensive software tool chain and intellectual property (IP) core for RISC-V designs.

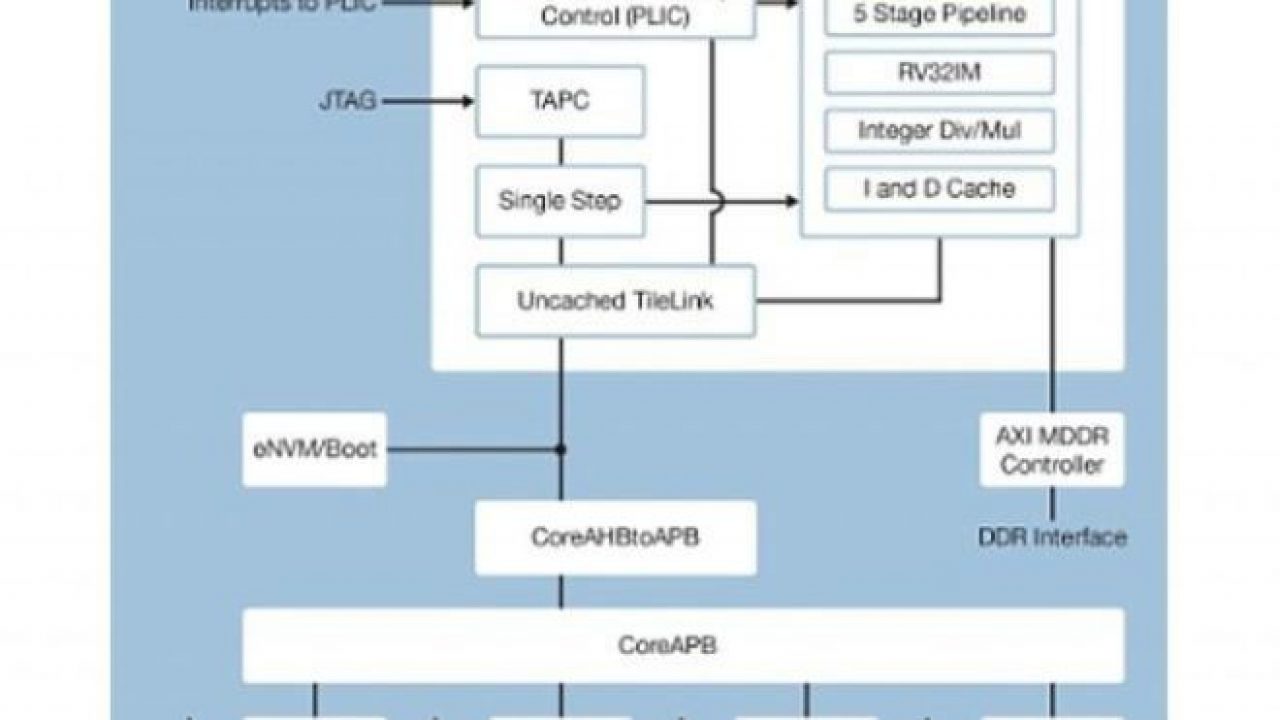

The company's RV32IM RISC-V core is available for Microsemi's IGLOO 2 FPGAs, SmartFusion 2 system-on-chip (SoC) FPGAs or RTG4 FPGAs, with an Eclipse-based SoftConsole integrated development environment (IDE) hosted on a Linux platform and the Libero SoC Design Suite providing full design support.

Microsemi's new RV32IM RISC-V core, developed in collaboration with SiFive, enables customers to design with an open instruction set architecture (ISA), enabling complete portability and a more secure processor architecture governed by a permissive BSD license. RISC-V is a new ISA which is now a standard open architecture under the governance of the RISC-V Foundation. RISC-V offers a soft processor solution for Microsemi's low power, reliable, secure FPGAs. The RV32IM RISC-V core unleashes a new generation of innovation for embedded designers.

The combination of Microsemi's IGLOO2 FPGA, SmartFusion2 SoC FPGA or RTG4 FPGA and its Libero SoC Design Suite create an ideal platform to target a RISC-V core for many embedded applications and is easy to implement with regard to size and power. The lower power and security of Microsemi's FPGA families provides a sound architecture for customers seeking to protect their IP and ensure long-term support for their designs in the industrial, defence, security and medical markets. The Libero SoC Design Suite allows designers to implement their designs and efficiently pack the FPGA logic elements (LEs), while the Eclipse-based SoftConsole IDE running on Linux allows users to compile and debug their source code.

Subscribe to Newsletter

Test Qr code text s ss