Intel exec sees huge potential for Moore’s Law post-CMOS

Article By : Rick Merritt

Moore’s Law has a long life, but pure vanilla CMOS process technology, not so much, a top fab executive from Intel said. During his keynote speech at the International Solid-State Circuits Conference (ISSCC) attended by nearly 3,000 chip designers, William Holt said: “The economics of Moore’s Law are sound if we focus on reducing cost […]

Moore’s Law has a long life, but pure vanilla CMOS process technology, not so much, a top fab executive from Intel said. During his keynote speech at the International Solid-State Circuits Conference (ISSCC) attended by nearly 3,000 chip designers, William Holt said: “The economics of Moore’s Law are sound if we focus on reducing cost per transistor.” But “beyond CMOS we’ll see changes in everything, probably even in computer architecture.”

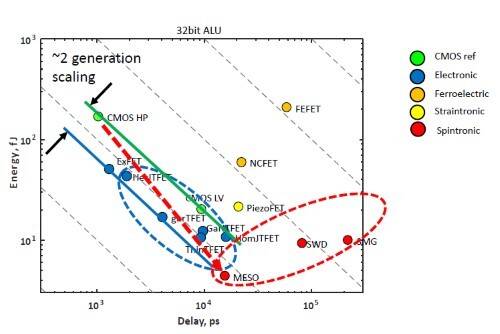

The GM of Intel’s technology and manufacturing group declined to share his thoughts about which among the “rich variety” of post-CMOS technologies chip makers will use or when. New techniques span tunneling FETs, ferroelectric FETs, spintronics, new III-V materials and more.

Holt: Beyond CMOS we’ll see changes in everything.

Holt did assert the new techniques won’t be in Intel’s 10nm process in which Intel is now prototyping its next-generation processors. In general, engineers will stretch CMOS as far as possible. Longer term, chips will be hybrids of different techniques blended with traditional CMOS.

“We will see a mixed mode operation parts [of the wafer] with CMOS and new devices on same wafer optimised for different benefits,” he said.

Holt put a positive spin on what is clearly a huge research effort ahead blazing a path for semiconductors in the next decade.

“I can’t tell you which of these [post-CMOS] technologies will be first or best but when we see this richness [of possibilities] that provides a wealth of opportunities over the next few years to make the tremendous progress needed in how to architect our parts,” he said. “It’s your challenge to figure out how to make them.”

The big challenge is that so far all the post-CMOS alternatives help reduce power consumption, a top concern, but they also run significantly slower than CMOS circuits. Holt compared this problem to the new complexity CMOS required a generation ago when engineers shifted to it from bipolar, responding to pressing power needs of the time.

A variety of post-CMOS technologies can lower power, but they cause delays. (Images: EE Times)

Holt said the industry needs to keep a focus on keeping power down and reducing cost per transistor. He reiterated Intel’s claim it has reduced cost per transistor at its 22nm and 14nm nodes at a rate slightly better than the industry’s 30 per cent historical trend. That’s despite the fact the cost of developing each new process has risen to 30 per cent in the last few nodes up from a historical trend of 10 per cent.

Subscribe to Newsletter

Test Qr code text s ss