Blog: Body Bias Gets Its Own Book

Article By : Junko Yoshida

The authors of The Fourth Terminal: Benefits of Body Biasing Techniques for FD-SOI Circuits and Systems make the case for body biasing, describing it as “a new and efficient tuning knob.”

I once wrote a blog — back in 2015 — pointing out:

As a reporter, I’ve never covered a technology that generates more geographically-divided perceptions, innuendo, and controversy among semiconductor engineers than FD-SOI.

I was referring to the race between FD-SOI and FinFETs. I was frustrated then because despite all the FD-SOI business and technology development stories I picked up as I traveled the “outside” world from Shanghai to Grenoble, FD-SOI got little traction in Silicon Valley. In America, the technology was a decided underdog. Intel, TSMC and even Samsung continued to forge ahead in pursuit of FinFETs as the only path forward to achieve more processing power via ever finer process nodes.

However, since the market began clamoring for ultra-low-power IoT and 5G devices, the industry is singing a different tune. Given much tighter cost and power requirements for such devices, semiconductor companies today accept that they need an alternative to FinFETs. CMOS integration has reached the limit for planar silicon process. Chip designers have embraced the idea that FD-SOI and FinFETs can play complementary roles.

More important, as more FD-SOI chips emerge, designers realize that one unique feature of the FD-SOI technology is its ability to use a wide body-bias range to modulate the transistor VT.

Designers are familiar with the concept of body biasing. They have been using it in different forms for many years in bulk CMOS technology. But a wave of new FD-SOI devices has reminded chip designers how effective body-biasing technology can be, for example, in creating an ultra-low-leakage sleep state for IoT devices.

In a new book, The Fourth Terminal: Benefits of Body Biasing Techniques for FD-SOI Circuits and Systems, published by Springer, the authors make the case for body biasing, describing it as “a new and efficient tuning knob” that should be added to every chip designer’s tool box. With body biasing, they wrote: “the circuit designers can efficiently modulate on the fly the transistor’s threshold voltage variation by software commands.”

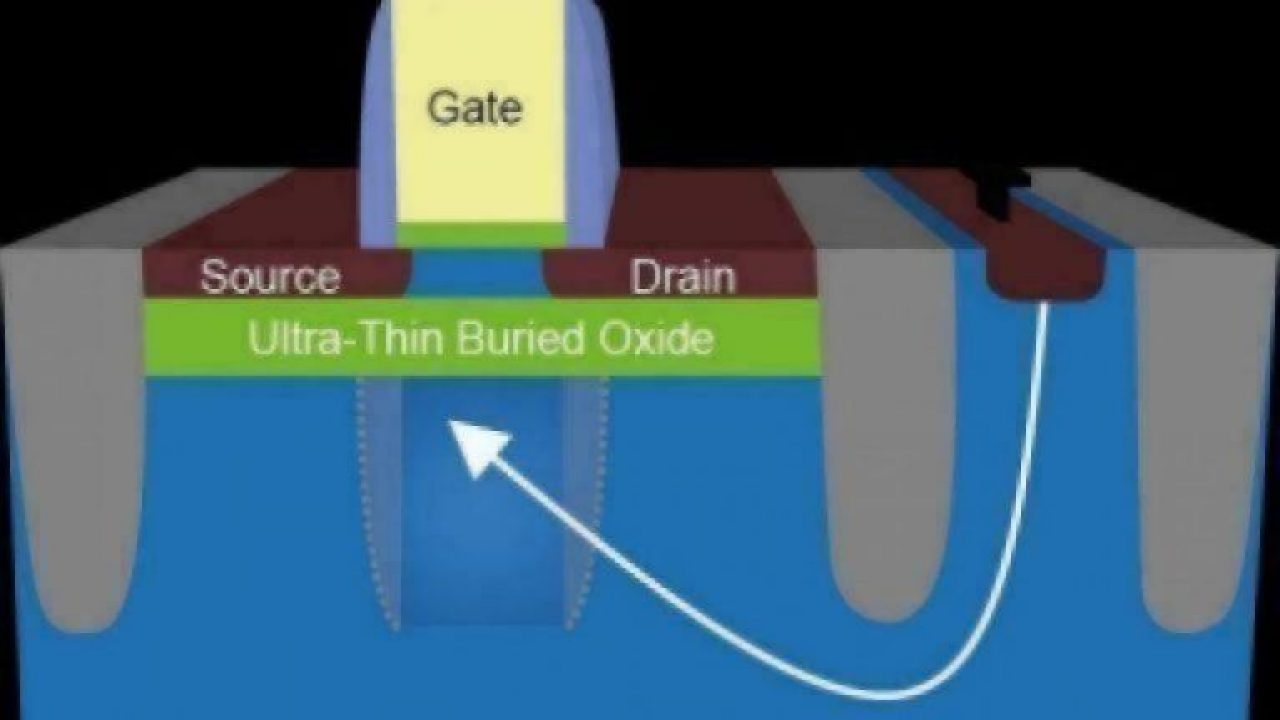

So, what does “the fourth terminal” mean? The authors explain that transistors now have four effective terminals: source, drain, gate and body, the volume underneath the conduction channel. “In FD-SOI, by applying a voltage bias on the latest [the volume underneath the conduction channel], one can efficiently vary the transistor’s threshold voltage.”

Acknowledging that the body-biasing technique is not new, the authors stress that “it is the first time [body biasing] can be deployed with a larger electrical impact into commercial CMOS technology.”

The first scientific book on FD-SOI design, covering both design techniques and industrialization aspects, The Fourth Terminal is highly technical, written for designers.

The book

- Provides readers with a single-source reference to Body-Biasing Techniques for FD-SOI Circuits and Systems

- Describes integrated circuit design techniques specific to deep submicron Ultra-Thin Body and Box (UTBB) Fully-Depleted Silicon on Insulator (FD-SOI) CMOS technology

- Presents the first coherent collection of FD-SOI-specific design techniques, for applications ranging from analog, RF, and mmW to SRAM design, embedded power management, and energy-efficient digital design

Andreia Cathelin

Three design experts at STMicroelectronics, including Fellow Andreia Cathelin, have co-edited and written chapters for The Fourth Terminal. The book will be an addition to Springer’s prestigious series “Integrated Circuits and Systems,” edited by professor Anantha Chandrakasan from MIT.

The book is available for order now and will be on show during ISSCC next week (Feb 15th).

Subscribe to Newsletter

Test Qr code text s ss