Europe Looks to the Future of Computing

Article By : Nitin Dahad

Europe's high-performance computing community convened in Valencia, Spain, last week to explore the strategy for Europe to remain competitive in addressing next generation embedded systems...

LONDON — The European Network on High Performance and Embedded Architecture and Compilation (HiPEAC) presented a strategy for Europe to remain competitive in addressing next generation embedded systems as part of its Vision 2019 report at its 14th conference on the future of computing last week in Valencia, Spain.

With most European semiconductor manufacturers not going into sub-10nm technology, Europe has an opportunity to exploit more mature technology nodes while continuing to research post-CMOS technologies and alternative, non-von Neumann architectures to address higher performance and efficiency as computing becomes ever more pervasive in all aspects of society, especially with the growth of machine learning and artificial intelligence, according to the report.

The HiPEAC Vision 2019 report says the end of computing as we know it represents an opportunity for Europe to steer the development of future systems that would respect the planet and humanity. It’s not going to be possible to continually shrink components while increasing performance, so accelerators need to be developed for specific application domains as the short-term route to performance gains, while researchers investigate new paradigms such as neuromorphic and quantum computing — which will complement, rather than replace, silicon semiconductor technology.

Modern computing systems now consist of multiple heterogeneous cores and memories programmed in a multitude of programming languages. The end of Dennard scaling points towards more heterogeneity at both the hardware and the software level.

The current approach to managing this increased complexity — adding layers of abstraction — has reached its limit, due to the inefficiency introduced by each additional layer and the lack of global optimization, according to the report. Even if complexity reductions are achieved with local optimizations, these will be seized upon to build even more complex systems.

The only way forward is to find practical and efficient solutions to deal with the increasing complexity. This includes automating the design of hardware platforms using AI-related techniques (the Electronics Resurgence Initiative (ERI) from Darpa is considered a step in that direction) and making use of open-source designs that are easily amenable to adaptation. Open source solutions enable the code — including the code generating hardware — to be inspected for bugs by a large community, which helps builds trust and democratizes access to and creation of new system solutions.

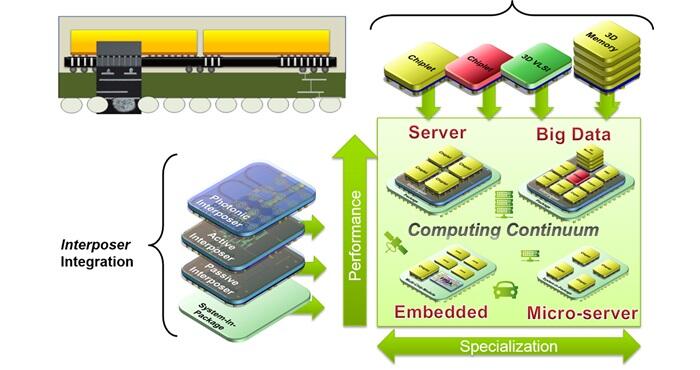

This smarter way of working would involve defining and allowing the reuse, integration and orchestration of white, black and grey boxes in a coherent way and with enough guarantees (security, reliability, bug-free). At the hardware level, a library of silicon blocks (chiplets) with a shared interfacing method could be developed, transposing the approach of printed circuit board and components to the micro-scale using interposers — the new PCB — and chiplets.

A key recommendation in the HiPEAC report is that software should be written by software, not programmers. Writing quality code for modern general-purpose processors is already very challenging for qualified humans — it is beyond the capacity of humans to develop correct, efficient, and secure code for new-generation heterogeneous computer platforms, particularly in a viable way for lead time and cost. The only long-term solution, according to the report, is to develop production environments capable of automatically generating and optimizing code out of a wide range of high-level specifications either written in a domain specific language or codified in a large and comprehensive labelled data set for machine learning.

In addition, computing infrastructure needs to be treated as a continuum, from the edge to the cloud, ensuring both interoperability between the individual sub-systems, as well as ensuring that devices can dynamically and intelligently adapt. Systems range from deep-edge (microcontrollers linked to sensors or actuators), to edge, concentrators, micro-servers, servers and cloud or HPC.

Hardware Alternatives

Today's advanced CMOS technology — even if density is increased — provides only slight performance improvements and requires huge investments in manufacturing and chip design. Hence it is not clear if the cost per transistor will still decrease. More mature technology (above 10nm) will be less expensive while still having the right density and performance for certain applications. For example, further low-power consumption can be achieved by controlling the bias in fully depleted silicon on insulator (FDSOI) technology, making it suitable for IoT devices which require ultra-low power in standby/active listening mode, but high performance when fully activated.

The use of interposer and chiplet technology will enable a reduction in design costs and the mixing of different technologies, such as analog, power converters and digital. It might become the sweet spot for edge devices, having the best performance/cost ratio. Europe should therefore continue investing in those technology nodes in order to expand their efficiency and usefulness for devices, and not only at the edge, according to the HiPEAC report.

Europe should also encourage architectural development based on less aggressive technologies — such as the Chinese supercomputer Sunway TaiHuLight, which was created using chips based on processes higher than 10nm technology.

An example of 3D stacked chip. (Source: LETI)

Post-CMOS technology research should continue not to substitute advanced CMOS, but to complement it, allowing growth in performance and efficiency. A fast transition from research to industrialization should be also encouraged. These post-CMOS technologies might also be a good source of the innovative sensor/actuator/interface technologies that will play a crucial role in future cyber-physical systems (CPS) and wireless sensor networks.

Innovative alternative architectures (non-von Neumann systems) are also addressed in the report. Processing should be near data (computing near or in memory) and the communication bandwidth should be increased for some applications, the report concludes.

New computing models can be efficiently applied to specific applications and they could lead to benefits because of the slowdown in performance increase of general-purpose programmable processors. One example is the forthcoming Configurable Spatial Accelerator from Intel, which is being described as a dataflow engine rather than an x86 or classical von Neumann system.

In the context of high-performance computing, networking and big-data applications, heterogeneous integration and modular stacking is gaining more and more interest. One example is 3D-stacking, which allows the density of transistors to continue increasing, not because of technology scaling, but by using the third dimension to stack dies of silicon one above another. This technology is already in use for some products but needs to be more widely developed to enable more diversity of chips at an acceptable cost.

Subscribe to Newsletter

Test Qr code text s ss